- Concepts uk Processor Registere and Instruction Execution Interrupts

- Memory hierarchy, Caching

- Input / Output

- Protection / Separation

### Instruction Execution Fetched instruction is braded into the Instruction Register (IR) page

- Processor interprets instruction in IR and performs one or more of the following actions

- Data transfer:

- Processor Memory

- Processor I/O

- Data processing: performing arithmetic / logic operations

- Control: an instruction may specify that the sequence of execution to be altered (comparable to an "If-then" or "goto" statement)

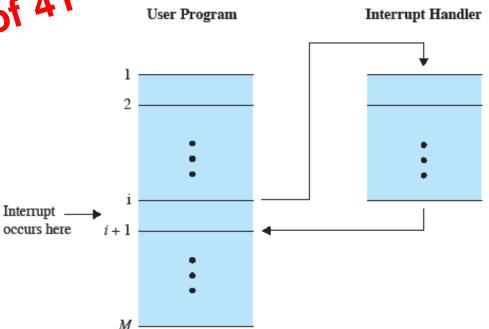

## Interrupt Handling

- Interrupts transfercentrol of to an interept handler (also called "Interrupt Service Routine")

- When an interrupt occurs, processor "jumps" to an interrupt handler

- An interrupt handler is program code that manages such an interrupt, is part of the overall operating system code

# • Is a hardware feature of 41 – Gachel containageopy of a portion of main memory

- - Processor first checks cache

- If data not found in memory, another portion of main memory has to be copied into the cache

- Invisible to the operating system

- Utilises the "Principle of Locality"

- Memory references by a processor tend to cluster

- Because of locality of reference, it is likely that many of the future memory references made by the processor will succeed with the current cache content

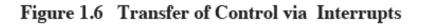

- Multicore Systems

A processor that multiple processing cores

Parallelism on the processor chip itself

- Each core has all the components of a single processor

- Performance advantages

- Multiple processors on a single chip brings huge performance advantages

- Introduction of different levels of cache memory