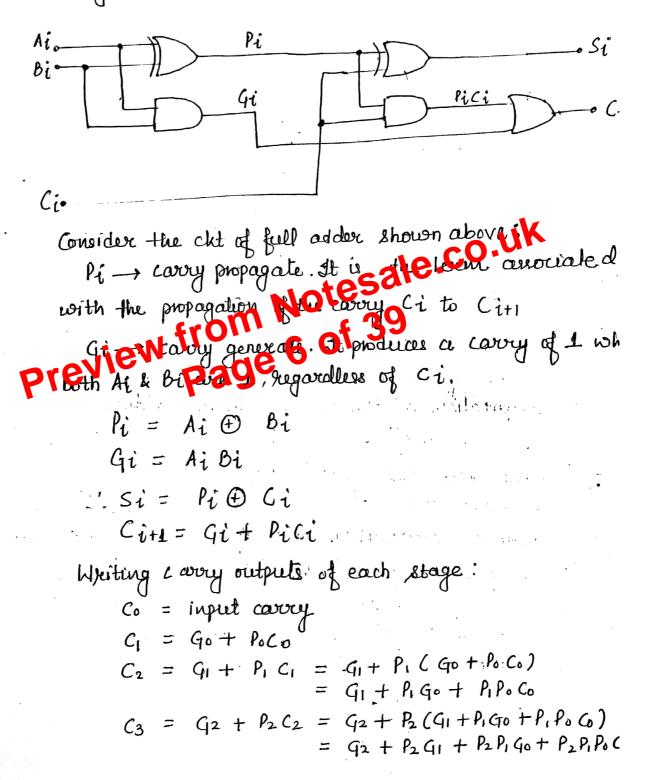

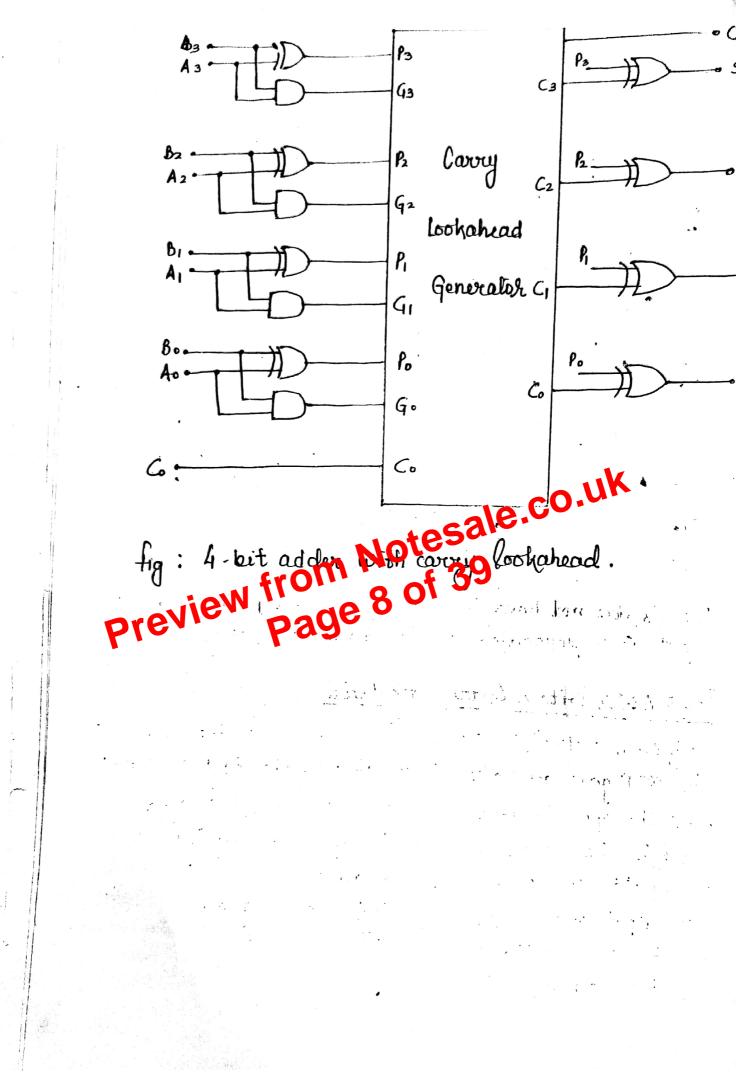

To reduce carry propagation delay time: — employ faster gates with reduced delays — invease equipment complexity in such a way that the carry delay time is reduced.

Covry Lookahead is one such technique for reducing the propagation time.

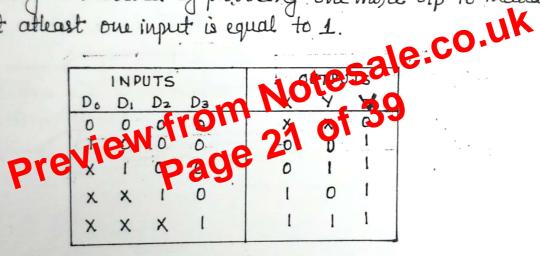

PRIORITY ENCODER

In the encoder defined above if D3 & D6 are 1 simultaneously, the output will be III because all three outputs are equal to 1. This (III) does not represent either kinary 3 or 6.

The priority encoder establish an input preiority to ensure that only one input is encoded. If higher preiority is given to inputs with higher subscript nos, & if both D3& D6 are 1 at the same time, the 0/p will be 110 because D6 has higher priority than D3.

Another ambiguity in the octal to binary encoder is that an o/p with all 0's is generated when all the inputs are 0; this o/p is the same as when Do is equal to 1. This discripency is resolved by providing one more o/p to indicate that atleast one input is equal to 1.

V → valid bit indicator. It is I when one or more inputs are equal to I.

If all inputs are 0, there is no valid input & V = 0.

X → in the input column & represents either I or 0.

ie ×100 represents the two minteens 0100 & 1100.

Priority level: D<sub>3</sub> > D<sub>2</sub> > D<sub>1</sub> > D<sub>0</sub>

The maps for simplifying outputs x & y can be derived by replacing each X in a row first by 0 & then by 1.

Logic Function Generation for using the multiplexer as a logic element, either the TT or one of the std forms of logic expression must be available.

Ex: Implement the expression using a multiplexer  $F(A, B, C, D) = \Sigma m(0, 2, 3, 6, 8, 9, 12, 14)$

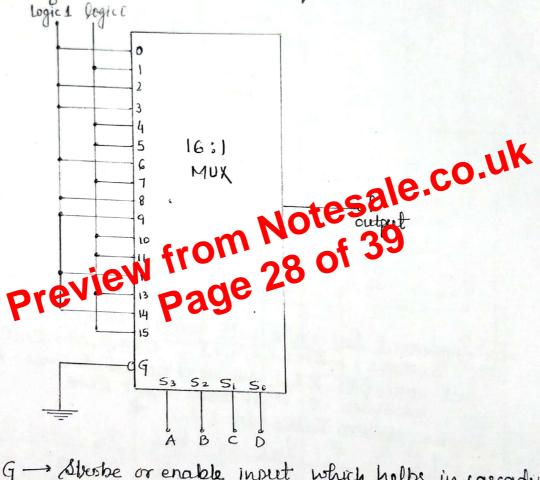

Sol: Since there are 4 variables, therefore, a MUX with four select inputs is required.

G→ Stesse or enable input which helps in cascading & it is generally active - low, which means it performs its intended operation when it is low.

Ex: Implement the previous function using 8:1 MUX. Sol: F(A, B, C, D) = Em(0, 2, 3, 6, 8, 9, 12, 14)

Ex: An 8:1 MUX has inputs (B, A connected to selection lines S2, S, and So resp! The data inputs Io through I7 are!  $I_3 = I_5 = I_7 = 1$ a)  $I_1 = I_2 = 0$  $I_6 = D$ Io = I4 = D Det the Boolean function that the MUX implements. Sol: Implementation table can be constructed from the given result ABC I3 I4 I5 I6 I7 Solved too 12 1 Ic (12) 6 8 (10) (4) BEBAB (D 4 2 0 D 0 13 (15) Ð 9 (i)instead of 5 3 (I)DI DCBA. D D 1 1 0 D 0 The SOP is obtal by the above table by writing the circled term as follows :- $F(A, B, C, D) = \sum m(1, 6, 7, 9, 10, 11, 12, 14, 15)$ This is the function, implemented by the 8.1 MUX. b)  $I_0 = I_3 = I_5 = I_6 = I_7 = 0$ I4 = D Here, the implementation to 32 & shown below. I 2=1 MSB variable chosen for application of the inputs is the PIEL I DADET The variable chosen Solved too (4) 6 7 5 3 2 DCB+ 1 DO 0 14 15 13 ok 12 (0) 11 (9) 8 D 1 0 OD O1 0 D 0 Having completed the thight now, relevant entreiles in the first and second rows are highlighted. The Boolean exp. can now be wreitten as  $Y = \Sigma m(2, 4, 9, 10)$ = DCBA + DCBA + DCBA + DCBA = CBA + DCBA + DCBA.