### GENERAL INSTRUMENT CP 1600 => 16- bit Processor

Third generation microprocessors

- After 1978 •

- 16-bit processors designed using HMOS(High density MOS) •

- High packing density and better speed power product •

- Provided with 40/48/64 pins package •

- Strong processing capability •

- Easier to program •

- Allowed dynamic relocation with an internal register size of 8/16/32 bits •

- •

- ٠

- Powerful interrupt handling capability Examples  $\rightarrow$  INTEL 808 & 8088 PINTEL 8088 PIN •

- •

- $4004 \rightarrow$  In 1971 first microprocessor was developed by INTEL. It contained approximately 2300 PMOS transistors. It was four bit device used in calculators.

- $8008 \rightarrow$  In 1972 INTEL developed a eight but microprocessor. It required 20 or more additional • devices to form a functional CPU.

- $8080 \rightarrow$  In 1974 INTEL developed 8080 which had much larger instruction set than 8008 and • require only two additional devices to form a functional CPU. Also 8080 used NMOS transistors. So it can operate much faster than 8008. It requires +5V, -5V, and +12V supplies.

- $MC6800 \rightarrow$  To avoid difficulties in 8080 which require different power supplies. Motorola came • out with MC6800 which requires only +5V supply. For several years 8080 and 6800 were top selling 8-bit processors.

- $8085 \rightarrow$  It is a 8-bit processor. INTEL produced 8085, an upgrade of 8080, requires only +5V • supply.

- MC6809  $\rightarrow$  Motorola then produced MC6809 which has few 16-bit instructions but thil basically 8-bit processor.

- 8086  $\rightarrow$  In 1978 INTEL developed 8086 which stuff 29,000 transistors and is fabricated using 1 Nos technol processor, it contains approximately 14 of 5

## Preview UNIT-1 8086 MICR

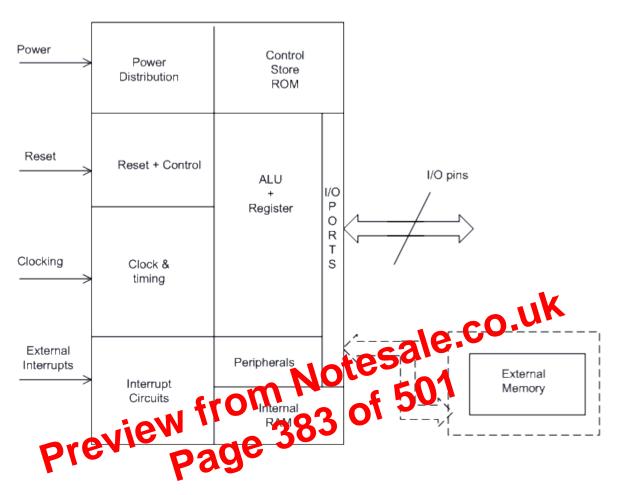

### -Typical Microprocessor based system

A typical microprocessor based system consists of

- CPU (central Processing Unit)

- (ALU + Register organization + Control unit)

- ➢ Timing unit

- ➢ Bus control logic

- Memory  $\geq$

- ➢ I/O subsystem

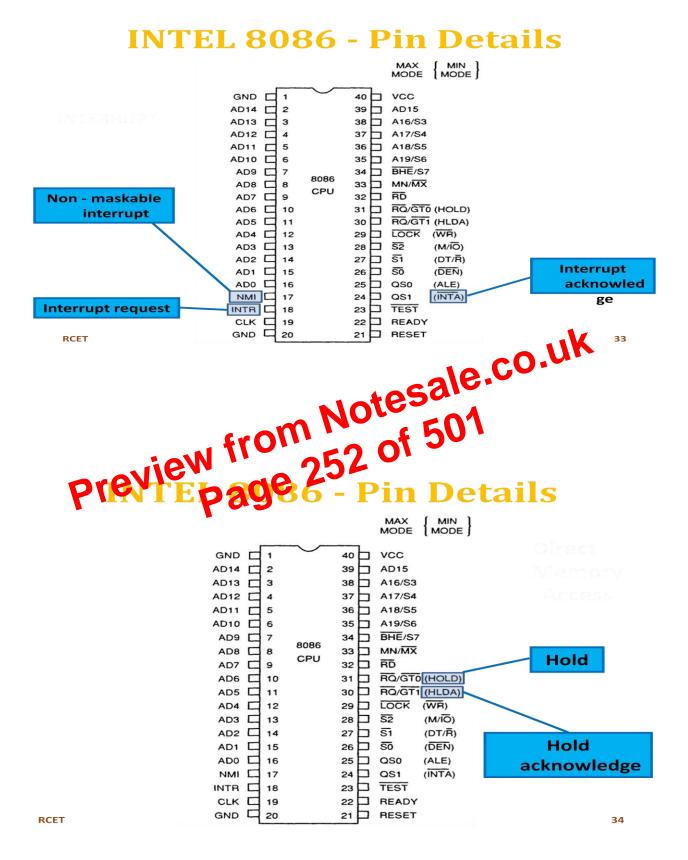

### Features of 8086

Introduced in 1978.

- Comes in Dual-In-Line Package(DIP) IC. ٠

- 8086 is a 16-bit N-channel HMOS microprocessor.

- Works on 5 volts power supply and draws a current of 360 ma, with an internal circuitry made up of 29K transistors.

- It consists of an electronic circuitry built using 29000 transistors. ٠

- It is built on single semiconductor chip and packaged in an 40-pin IC. ٠

- It has 20-bit address bus and 16-bit data bus. ٠

- It can directly address upto  $2^{20}$  I.e., 1M bytes of memory. ٠

- The 16-bit data word is divided into lower-order byte and

higher order byte.

- The 20-bit address bus is time multiplexed:

- The lower order 16-bit address bus is time multiplexed with data bus. CO. UK The higher order 4-bit address bus is time and the CO. CO. UK  $\geq$

- tatus signals.  $\triangleright$

- The maximum internal clock f

- 8086 chip do e the facility of internal clock generation.

(the IN EL 8284 clock general of the sused to generate the clock signal for 8086 microprocessor

- The clock signal is divided by 3 in case of 8086 for internal clock requirements.

- 8086 uses I/O mapped I/O techniques hence I/O devices are accessed by using separate 16-bit address

- 8086 operates in two different modes

- ✤ Minimum mode

(It works as a simple single processor system when configured in minimum mode)

✤ Maximum mode

(It works as a multiprocessor system i.e., along with math coprocessor and I/O coprocessor when configured in maximum mode)

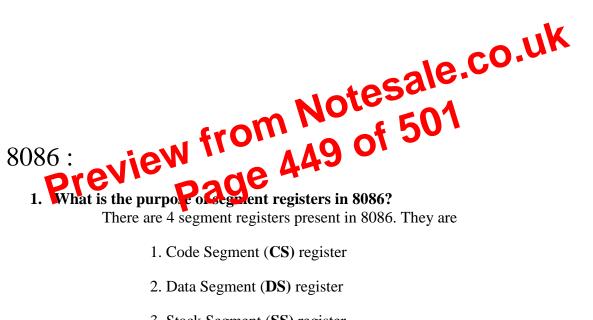

### **8086 Registers**

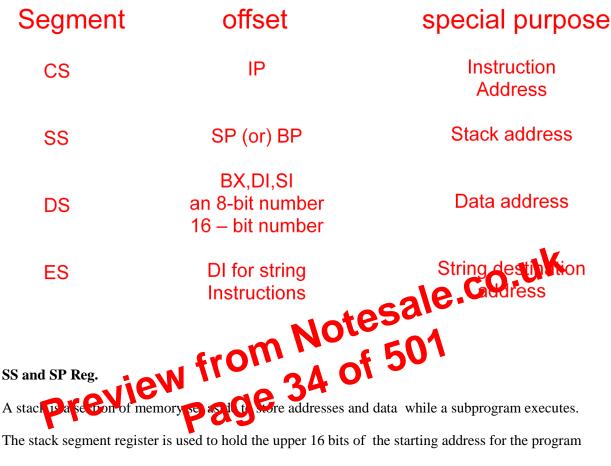

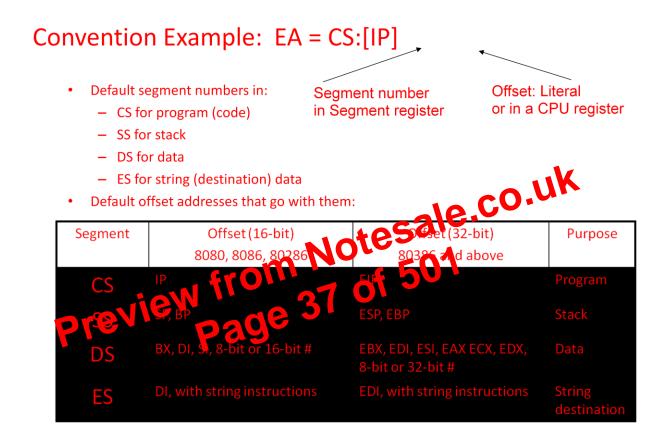

8086 - Default 16 bit segment and offset address combinations

stack.

- 2 Logical Addresses for each Segments.

- Base Address (16 bits)

- Offset Address (16 bits)

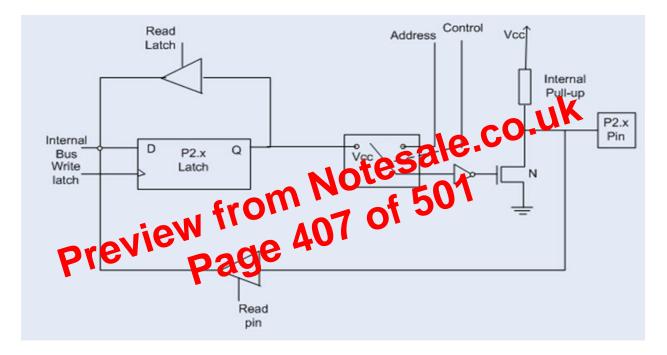

- Segment registers are used to store the Base address of the segment.

### **Stack Pointer Register**

A Stack, is a section of memory set aside to store addresses and data while asubprogram is being executed. An entire 64 K bytes segment is set aside as Stack in 8086MPU. The upper 16 bits of the starting address for this segment is kept in the stack segment register. The Stack Pointer (SP) register contain the 16-bit offset from the start of the segment to the memory location where a word was most recently stored on the Stack. The memory location where a word was most recently stored is called the top of Stack .Fig.6 shows the details.The physical address for a stack read or for a stack write is produced by adding the contents of the stack pointer register are shifted four bit positions left and the contents of SP are added to the shifted result. In the figure 5000 H in SS is shifted

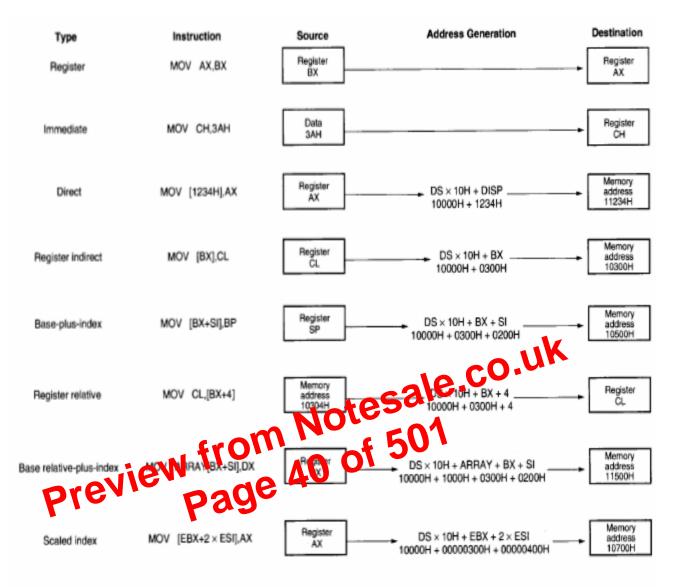

Notes: EBX = 00000300H, ESI = 00000200H, ARRAY = 1000H, and DS = 1000H

FIGURE 3-2 8086-Pentium 4 data-addressing modes.

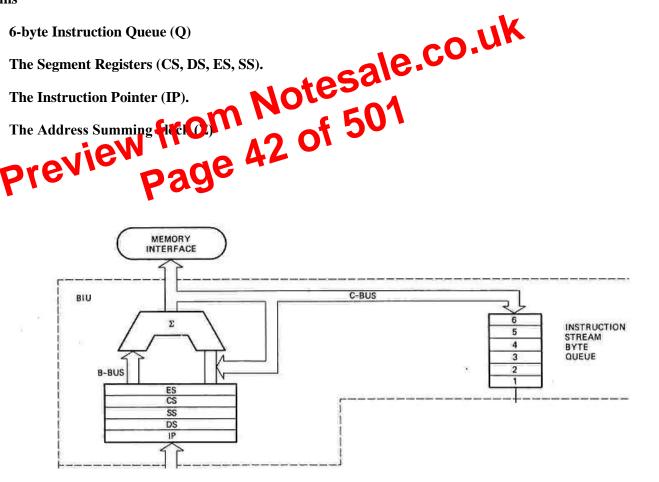

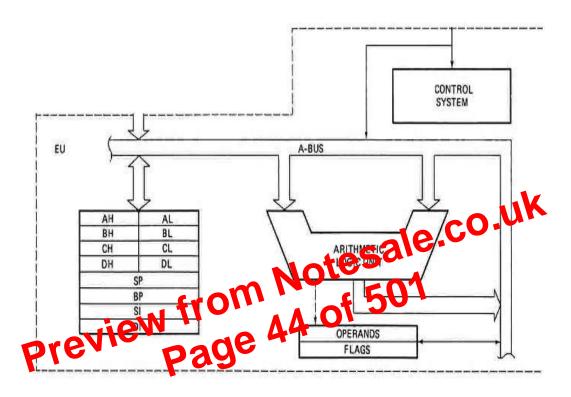

- The BIU performs all bus operations such as instruction fetching, reading and writing • operands for memory and calculating the addresses of the memory operands. The instruction bytes are transferred to the instruction queue.

- EU executes instructions from the instruction system byte queue. •

- Both units operate asynchronously to give the 8086 an overlapping instruction fetch and ٠ execution mechanism which is called as Pipelining. This results in efficient use of the system bus and system performance.

- BIU contains Instruction queue, Segment registers, Instruction pointer, Address adder. •

- EU contains Control circuitry, Instruction decoder, ALU, Pointer and Index register, Flag register.

### **BUS INTERFACE UNIT (BIU)**

### Contains

- •

- Instruction decoder

- ALU

### **EXECUTION UNIT – General Purpose Registers**

- <u>Register Addressing Mode.</u>

- <u>Direct addressing Mode.</u>

- <u>Register Indirect Addressing Mode.</u>

# **Immediate Addressing Mode**

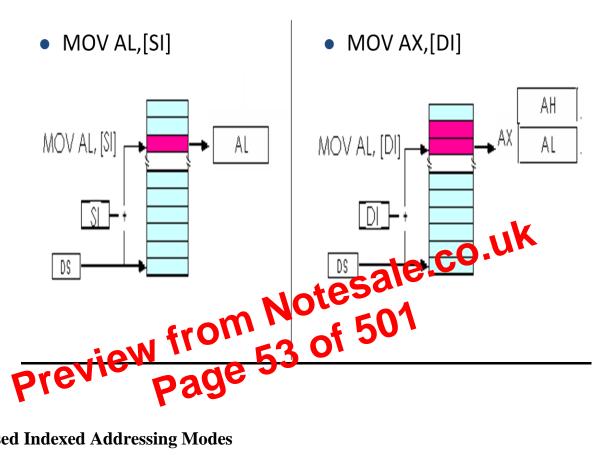

# **Indexed Addressing Mode**

### **Based Indexed Addressing Modes**

The based indexed addressing modes are simply combinations of the register indirect addressing modes. These addressing modes form the offset by adding together a base register (bx or bp) and an index register (si or di). The allowable forms for these addressing modes are

mov al, [bx][si] al, [bx][di] mov al, [bp][si] mov al, [bp][di] mov

Suppose that bx contains 1000h and si contains 880h. Then the instruction mov al,[bx][si]

would load al from location DS:1880h. Likewise, if bp contains 1598h and di contains 1004, mov bits in ax from locations SS:259C ax,[bp+di] will load the 16 and SS:259D.

The addressing modes that do not involve by use the data segment by default. Those that have by as an operand use the stack segment by default.

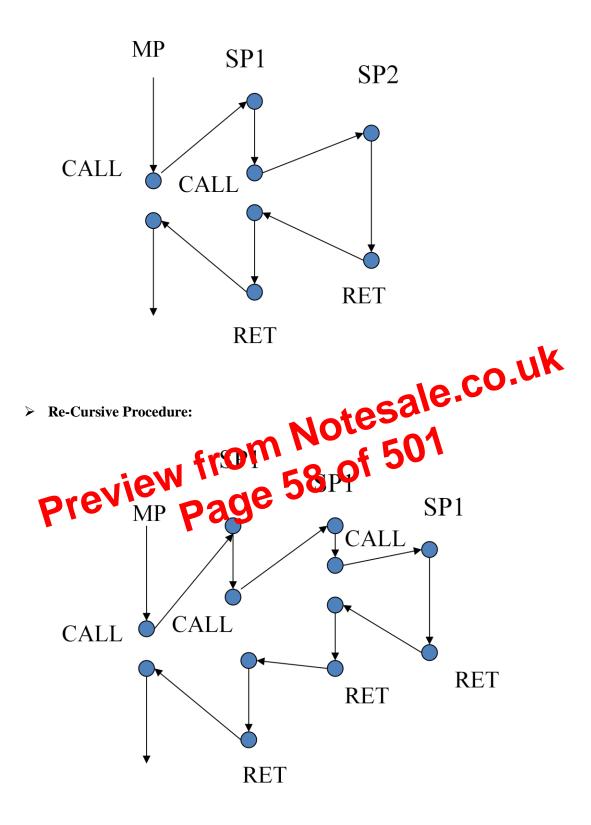

> The recursive procedures are implemented using procedure CALL itself, but care must be taken to assure that each successive call does not destroy the parameters and results

**Code SEGMENT**

**ASSUME CS : Code, DS : Data**

**START : Mov AX, Data**

Mov DS, AX

:

Mov AX,Num

CALL X1

INT 3H

X1 PROC Near

**MOV BX,Num**

RET from Notesale.co.uk Bage 60 of 501 Code ENDS Preveiev

**END START**

> Using (General purpose CPU Registers) Registers:

**Code SEGMENT**

**ASSUME CS : Code**

START : Mov AX, 2234H

### Mov BX, 3342H

:

CALL X1

:

INT 3H

### X1 ENDP

**Code ENDS**

**END START**

> Passing parameters using pointers passed in registers:

:

Mov SI, OFFSET Str1 Mov DI, OFFSET Str2 : CALL X1 : INT 3H X1 PROC Near Mov AL, (SI) Mov BLeaLOM 62 0f 501 Mov BLeaLOM 62 0f 501

RET

X1 ENDP

Code ENDS

### **END START**

- > Features of Passing parameters using global variables:

- o Extra memory required.

- o All the globally declared variables need to be remembered.

- o Modification of parameters cannot be done directly.

- o Can be implemented only by using ASSEMBLER and not by any other means.

- > Features of Passing parameters using CPU Registers:

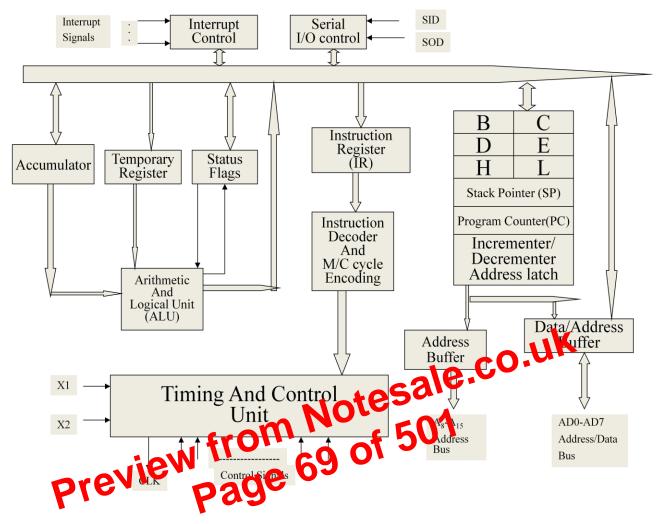

- ALU

- The arithmetic and logical unit(ALU), performs the following arithmetic and logical operations:

- > Addition

- > Subtraction

- Logical AND

- > Logical OR

- Logical Exclusive-OR

- Complement (Logical NOT)

- Increment (add 1)

- Decrement(Subtract 1)

# Functional unit of 8085

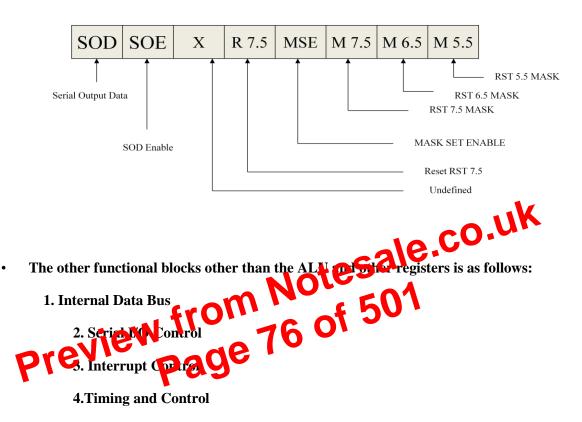

• Accumulator contents for a SIM instruction:

5. Address Buffer and Address / Data Buffer

> Internal Data Bus:

The internal data bus is 8-bits inside and carries instructions and data between the CPU registers.

- Functional unit of 8085

- Serial I/O Control :

Generally the Data flowing between microprocessor will be either parallel or serial, but for some devices it is necessary to accept data serially and output data serially and if there is a provision built in the microprocessor for this purpose it is very efficient.

In 8085 there is such provision through SID and SOD pins.

The SID pin is used for accepting serial data input.

The contents of stack pointer or program counter can be loaded into these buffers. These buffers drive the external address bus and address-data bus. The internal data bus is also connected to the address / data buffer to send or receive the data.

- **Data and Address Bus** •

- The INTEL 8085 is an 8-bit microprocessor. Its data bus is 8-bit wide and hence, 8 bits of data can be transmitted in parallel from or to the microprocessor.

- The INTEL 8085 requires a 16-bit wide address bus as the memory address are of 16-bits. ٠

- The 8 most significant bits of the address are transmitted by the address bus, A-bus (pins A8 - A<sub>15</sub>).

- The 8 least significant bits of the address are transmitted by Address / Data bus, AD- bus ( pins  $AD_0 - AD_7$ ).

- The Address / Data bus transmits data and address at different moments. At a particular • es in tin Otesale.co.uk Consists of on 4 moment it transmits either data or address. Thus the AD - bus operates in time shared mode. This technique is known as Time Multiplexing .

- **Pin Configuration Of 8085** •

- The logical pin out of an 8085 microproc ٠

- or can be categorized int the following groups: The pins of the 8085 mi

- hus

- Data bus

- **Control and Status signals**  $\geq$

- Power Supply and Frequency signals  $\geq$

- $\geq$ **Externally initiated signals**

- Serial I/O ports  $\geq$

Control and Status signals:

This group of signals includes two control signals ( RD

and WR), three status signals ( IO/M,  $S_1$  and  $S_0$ ) to identify the nature of the operation, and one special signal (ALE) to indicate the beginning of the operation. These signals are as follows:

ALE – Address Latch Enable:

**Output and Tri-stated line**

It is a Address Latch Enable signal. It goes high during the first clock cycle of a machine cycle and enables the lower 8 bits of the address to be latched either into the memory or external latch.

p control read operation Of 501 **RD** : Read Output and a tri-stated lin hen it goes n roprocessor reads the data from the selected memory ocation or an I/O device.

WR : Write

.

**Output and Tri-stated line**

It is a signal to control Write operation

When it goes low the microprocessor writes the data into the selected memory or I/O device.

IO/M : I/O or Memory indicator

**Output and Tri-stated line.**

It is a status signal which distinguishes whether the Address is for Memory or I/O.

When it goes high the address is for an I/O device and when it goes low the address on the address bus is for a memory location.

S<sub>1</sub> and S<sub>0</sub> : Bus state/ status indicator ٠

**Output lines.**

.

٠

The status output signals from microprocessor and these signals gives the information about the various types of operations that take place.

| $S_1$ | $S_0$ | Operations |

|-------|-------|------------|

| 0     | 0     | HALT       |

| 0     | 1     | WRITE      |

| 1     | 0     | READ       |

| 1     | 1     | FETCH      |

**Power Supply and Clock Frequency Signals**

- > VCC : + 5 V Power Supply

- The power supply and frequency signals are as for the COUK VCC : + 5 V Power Supply VSS : Ground Ind 2 of 501 VSS : Ground R onnections

**Input lines**

These are terminals to be connected to an external crystal oscillator which drives an internal circuitry of the microprocessor to produce a suitable clock for the operation of microprocessor.

CLK(Out) : Clock signal

**Output line**

It is a Clock Output for user, which can be used for other digital IC's. Its frequency is same at which processor operates.

**Externally Initiated Signals including Interrupts:** ٠

There are five Interrupt signals associated with 8085 microprocessor along with an acknowledge signal for these interrupts.

apart from the interrupt signals there are the following externally initiated signals associated with 8085 microprocessor pin configuration they are

HLDA : Output

It is a signal for HOLD acknowledgement. It indicates that the HOLD request has been received.

The HLDA goes low after the HOLD signal goes low.

The CPU takes over the buses after Half clock cycle of removal of HLDA signal.

• **READY** : Input

It is used by the microprocessor to sense whether a peripheral is ready to transfer data or not.

A slow peripheral may be connected to the microprocessor through the Ready line.

If READY is high the peripheral is ready. If it is low the microprocessor waits till it goes high.

• **RESET OUT : Output**

Indicates that CPU is being reseted, and is used by the meroprocessor to reset the other sub-systems in the microprocessor based system

• (RESET IN)' : Input

It resets they rogram counter or zono. Letso resets interrupt enable and HLDA flipflops. However, affect any other may be register except the instruction register. The CPU is held in the reset condition as long as RESET is applied.

• Serial I/O ports

The 8085 microprocessor has two signals for serial communication i.e., SID and SOD

SID: Serial Input Data (Input)

It is data line for serial input. The data on this line is loaded into the 7<sup>th</sup> bit of the accumulator when RIM instruction is executed.

SOD : Serial Output Data (Output)

It is a data line for serial output. The 7<sup>th</sup> bit of the accumulator is output on SOD line when SIM instruction is executed.

Simple programs on 8086 :

mov cx,0

mov dx,0

mov ax,num1 ;x1 \* y1

mul num2

mov res,ax

mov bx,dx

mov ax,num1 ;x1 \* y2

mul num2+2

add bx,ax

mov ax,num1+2 ;x2 \* y1 Notesale.co.uk mul num2 from 92 of 501 dd ex,ax age 92 of 501 mov res+2;bx

Pre'

add cx,dx

mov ax,num1+2 ;x2 \* y2

mul num2+2

add cx,ax

mov res+4,cx

mov res+6,dx

mov ax,4c00h

int 21h

code ends

Or

If READY pin is high, the peripheral is ready otherwise the 8086 enters wait state.

This state is used by slow peripheral devices. The peripheral devices can transfer the data to or from the microprocessor by using READY input line. The microprocessor remains in wait state as long as READY line is low. During the wait state, the contents of the address, address/data and control buses are held constant.

- 10. 8086 has \_\_\_\_\_20\_\_\_\_ address pins and \_16\_\_\_\_ data pins

- 11. Name different segments in 8086 microprocessor CS,SS,DS,ES

- 12. Name the index registers in 8086 microprocessor Source index, destination index

- 13. Each register in 8086 is of \_\_\_\_\_16\_\_\_\_ bit wide

15. what is the purpose of execution unit in 8086 microprocessor e.co.uk ANS: Write short note on the Execution Unit (N) n Bus Interface Unit (BIU). 8086 microprocessor has two upres Officeution Unic (HC) and Bus Interface Unit (BIU). They are dependent and ret worked by seen other Below is a short description of these two units

**Execution Unit (EU)**: Execution unit receives program instruction codes and data from the BIU, executes them and stores

the results in the general registers. It can also store the data in a memory location or send them to an I/O device by passing the data back to the BIU. This unit, EU, has no connection with the system Buses. It receives and outputs all its data through BIU.

<u>ALU (Arithmetic and Logic Unit)</u>: The EU unit contains a circuit board called the Arithmetic and Logic Unit. The ALU can perform arithmetic, such as,  $+, -, \times, /$ and logic such as OR, AND, NOT operations.

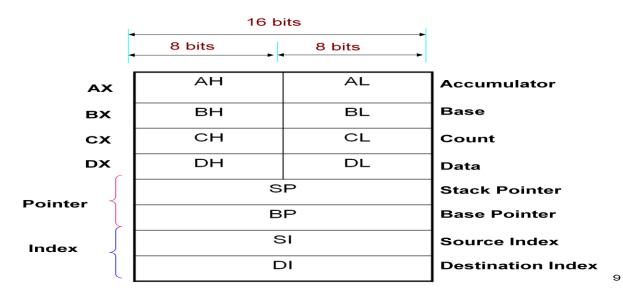

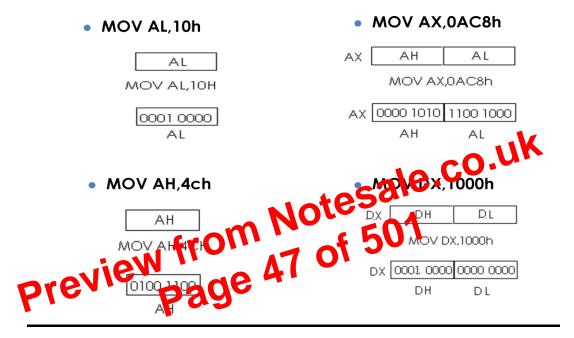

**<u>Registers</u>**: A register is like a memory location where the exception is that these are denoted by name rather than numbers. It has 4 data registers, AX, BX, CX, DX and 2 pointer registers SP, BP and 2 index registers SI, DI and 1 temporary register and 1 status register FLAGS . AX, BX, CX and DX registers has 2 8-bit registers to access the high and low byte data registers. The high byte of AX is called AH and the low byte is AL. Similarly, the high and low bytes of BX, CX, DX are BH and BL, CH and Cl, DH and DL respectively. All the data, pointer, index and status registers are of 16 bits. Else these, the temporary register holds the operands for the ALU and the individual bits of the FLAGS register reflect the result of a computation.

**Bus Interface Unit :** As the EU has no connection with the system Busses, this job is done by BIU. BIU and EU are connected with an internal bus. BIU connects EU with the memory or I/O circuits. It is responsible for transmitting data, addresses and control signal on the busses.

**<u>Registers</u>**: BIU has 4 segment busses, CS, DS, GOES. These all 4 segment registers holds the addresses of instructions moderate in memory. These values are used by the processor to access memory. Orations. It also contain 1 pointer register IP. IP contains the address of the metrification to executed by the EU.

**Instruction Queue :** BIP also ontain an instruction queue. When the EU executes instructions, the BIU gets up to 6 bytes of the next instruction and stores them in the instruction queue and this process is called instruction prefetch. This is a process to speed up the processor. Also when the EU needs to be connected with memory or peripherals, BIU suspends instruction prefetch and performs the needed operations.

\*\*\*\*\*

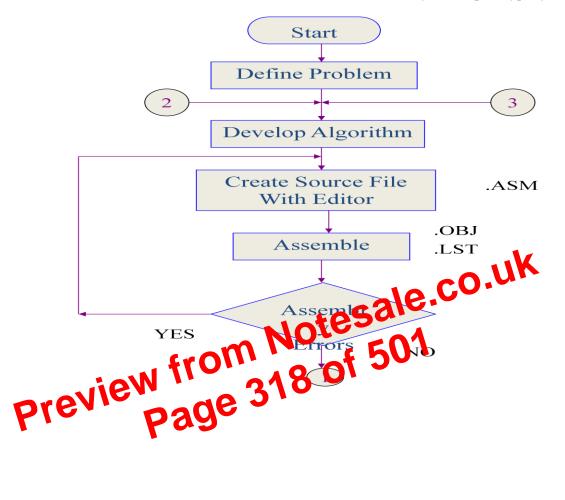

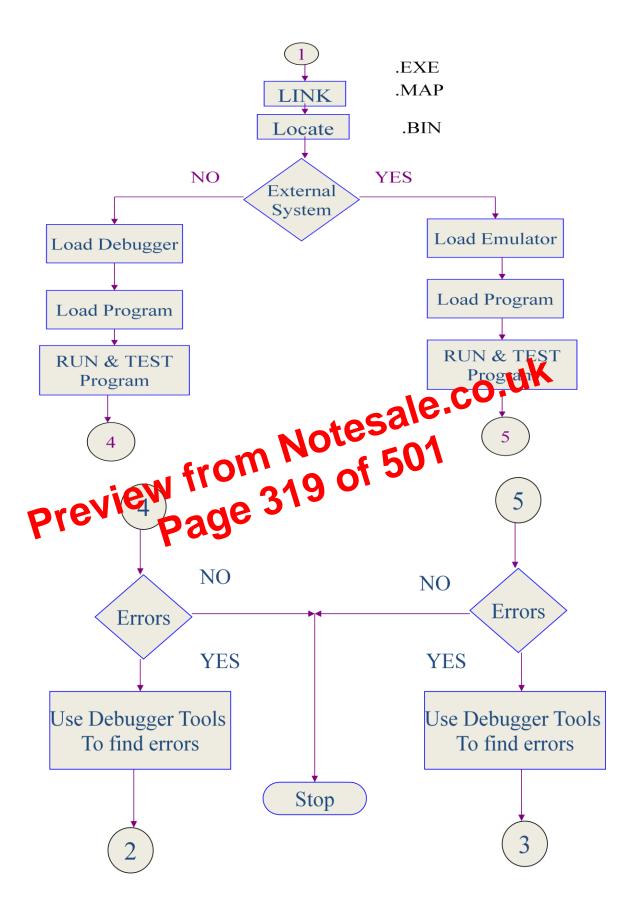

# **UNIT-2** Assembly language programming involves all the instructions :

Write ALP and execute the program to

1. Add two 8-bit numbers

2. Add two 16-bit numbers

- 3. Add two 32-bit numbers

- 4. Subtract two 8-bit numbers

- 5. Subtract two 16-bit numbers

- 6. Subtract two 32-bit numbers

- 7. Multiply two 8-bit numbers

- 8. Multiply two 16-bit numbers

- 9. Perform 8-bit division

- 10. Perform 16-bit division

- 11. Find square of a number

- 12. Find cube of a number

- 13. Exchange two numbers

### Experiment III, IV, V & VI: ARRAY PROGRAMMING

### Write ALP and execute the program to

- 14. Add a given series of numbers

- 15. Find average of a given series of numbers

- 20. Sort a series of given numbers in descending order 21. Find GCD of two given numbers in descending order 22. Find LCM of two given numbers 23. Display Filt

- 99 of 501

### **Experiment VII : BCD, DECIMAL, ASCII OPERATIONS**

Write ALP and execute the program to

- 24. Perform one byte BCD addition

- 25. Perform one byte BCD subtraction

- 26. Produce packed BCD from two ASCII characters

- 27. Convert decimal number to binary

- 28. Convert a binary number to a decimal number

### **Experiment VIII & IX : STRING MANIPULATION PROGRAMS**

- 29. Move a string of data bytes from one location to another

- 30. Concatenate two strings

- 31. Reverse a given string

- 32. Compare two strings

- 33. Find length of a given string

- 34. Find whether the given byte is in the string or not

- 35. Insert an element in a given string

6

5

4

Timers 0 of an 8253 provide the Transmit and receive baud clocks for the USART. (Refer to chapter 5 for a detailed discussion of the Hardware). This timer is initialized by the system firmware to provide proper baud clock based on the settings of the DIP Switch as shown below.

### **DIP SWITCH**

### 1. SW3 SW2 SW1 Baud rate

**OFF OFF ON 9,600\***

2. Memory selection:

ESA 86/88-2 has four sockets, labeled U9, U8, U7, U6 for RAM. These sockets are configured for 62256(32X 4) devices. Two of these sockets are populated (providing 64K Bytes of RAM) and two are for user expansion.

**DEVICE DIP SWITCH JUMPER**

Preview from Notesale.co.uk Page 113 of 501

3. Register Addressing Mode

Data is stored in a register and it is referred using the particular register Ex: MOV BX,AX

4. Register Indirect Addressing Mode

The offset address of data is in either BX or SI or DI register

Default segment is either DS or ES

EX: MOV AX,[BX]

5. Indexed Addressing Mode

Offset of the operand is stored in one of Index register

DS is default segment for index registers SI and DI

For Strings DS and ES are default segments for SI and DI

EX: MOV AX, [SI]

6. Register Relative Addressing Mode

default segment

ontent of my control of the registers BX,BP,SI and DI in Data is available at an effective address formed Gadding an 8 bit or 16 bit displacement with the conten

a ed Indexed Add

Effective address of data is formed by adding content of base register to content of Index register

Default segment register may be ES or DS

EX: MOV AX,[BX][SI]

8. Relative Based Indexed

EX

Effective address is formed by adding an 8 or 16 bit displacement with the sum of contents of any one of base registers (BX or BP) and any one of Index registers in a default segment

EX: MOV AX,50H [BX] [SI]

9. Intrasegment Direct Mode

Effective address to which the control is to be transferred is given by the sum of 8 or 16 bit displacement and current content of IP

| 1.4 8-BIT SUBTRACTION                                                        |

|------------------------------------------------------------------------------|

| .MODEL TINY                                                                  |

| .STACK 32H                                                                   |

| .CODE                                                                        |

| START:                                                                       |

| MOV AX,@DATA                                                                 |

| MOV DS,AX                                                                    |

| MOV AX,00                                                                    |

| MOV AL,NUM1                                                                  |

| MOV BL,NUM2                                                                  |

| SUB AL,BL                                                                    |

| MOV RESULT, AL                                                               |

| INT 3                                                                        |

| SUB AL,BL<br>MOV RESULT,AL<br>INT 3<br>.DATA<br>NUMI DB OFFH<br>NUM2 DB 0AAH |

| NUM2 DB 0AAH                                                                 |

| RESULT DB 00                                                                 |

| END START                                                                    |

| RESULT: 0FFH                                                                 |

| 0AAH                                                                         |

055H

### **1.7 8-BIT MULTIPLICATION**

.MODEL TINY

.STACK 32H

.CODE

START:

MOV AX,@DATA

MOV DS,AX

MOV AX,00

MOV AL,NUM1

MOV BL,NUM2

MUL BL

MOV RESULT, AL

MOV RESULT1,AH

INT 3

eview from Notesale.co.uk eview from 132 of 501 FH Page 132 of 501 AH

NUM2 DB 0AAH

RESULT DB 00

**RESULT1 DB 00**

END START

**RESULT: 0FFH**

0AAH

A956H

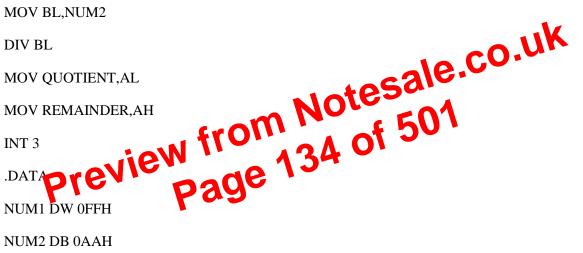

### 1.9 8-BIT DIVISION (16 Bit by 8 Bit)

.MODEL TINY

.STACK 32H

.CODE

START: MOV AX,@DATA

MOV DS,AX

MOV AX,00

MOV DX,00

MOV AX,NUM1

MOV BL,NUM2

DIV BL

MOV QUOTIENT, AL

MOV REMAINDER, AH

INT 3

NUM1 DW 0FFH

QUOTIENT DB 00

**REMAINDER DB 00**

END START

**RESULT: 0FFH**

0AAH

5501H QUOTIENT: 01H

**REMAINDER R: 55H**

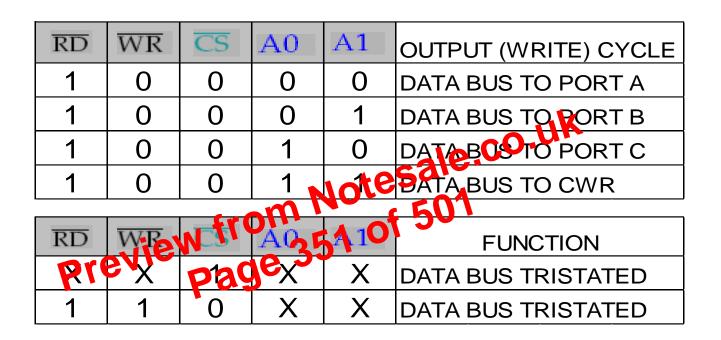

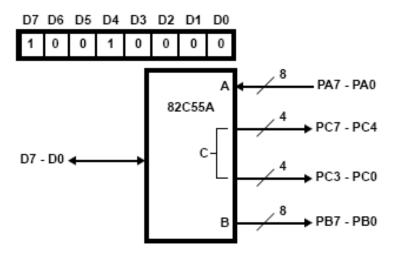

EX2: RAMP WAVE GENRATION USING DAC ;8086 MICROPROCESSOR ;INTERFACING TO 8086 WITH DAC INTERFACE ;PORT: PORTA USED ASOUTPUT

### CODE SEGMENT

**ORG 2000H** ASSUME CS:CODE MOV AL,80H ;INTIALIZE 8255PPI MOV DX,0FFE6H ;PORTA,PORTB,PORTC ARE OUTPUT OUT DX.AL :0FFE6H CONTAINS CWR OF 8255 MOV DX,0FFE0H ;0FFE0H INDICATES PORT w from Notesale.co.uk Page 169 of 501 MOV AL,00H REPEAT: OUT DX,AL CALL DELAY INC AL JMP REPEAT INT 3H DELAY PRO MOV CX,01FFH L1: NOP LOOP L1 RET DELAY ENDP CODE ENDS END

### **EX3: TRIANGULAR WAVE GENRATION USING DAC**

;8086 MICROPROCESSOR ;INTERFACING TO 8086 WITH DAC INTERFACE ;PORT: PORTA USED ASOUTPUT

| OR       | AL,BL    |                 |

|----------|----------|-----------------|

| RET      |          |                 |

| KSCAN    | ENDP     |                 |

| DELAY PR | ROC NEAR |                 |

| PUSH     | CX       |                 |

| MOV      | CX,0000H | ; DELAY ROUTINE |

| DLY: NOP |          |                 |

| LOOP     | DLY      |                 |

| POP      | CX       |                 |

| RET      |          |                 |

| DELAY    | ENDP     |                 |

| END      |          |                 |

Preview from Notesale.co.uk Page 172 of 501

| SM0 | SM1 | SM2 | REN | TB8 | RB8 | TI | RI |

|-----|-----|-----|-----|-----|-----|----|----|

|     |     |     |     |     |     |    |    |

- SMO & SM1 (Modes of Operation)

- o SM2 controls microprocessor to microprocessor communication

- REN (receive enable)

- o TB8 (Transmit bit 8)

- RB8 (Received bit 8)

- o TI (transmit flag)

- RI (Received Flag)

### MODES OF OPERATION

| SM1                                                                              | SM0 | MODE | OPERATION<br>Shift register, hand rate $= f/12$                          |  |

|----------------------------------------------------------------------------------|-----|------|--------------------------------------------------------------------------|--|

| 0                                                                                | 0   | 0    | Shift register, baud rate = $f/12$                                       |  |

| 0                                                                                | 1   | 1    | Shift register, baud rate = $f/12$<br>8 BIT UART, baud rate programmable |  |

| 1                                                                                | 0   | 2    | 9 BIT UART, and inte = $f/32$ , $f/64$                                   |  |

| 1                                                                                | 0   | 3    | S BIT UART, baud care Sogrammable                                        |  |

| • BAU frame $y = 2^{\text{SMOD}} * \text{Oscillator frequency}/(256-TH1)(12*32)$ |     |      |                                                                          |  |

• SMOD is bit 7 of PCON register

### **INTERRUPT STRUCTURE OF 8051**

There are 5 INTERRUPTS in 8051

- i. Timer Interrupts (TF0 & TF1)

- ii. External Interrupts (INT 0 & INT1)

- iii. Serial port Interrupt

RESET considered as 6<sup>th</sup> interrupt

### **RESPONSE TO INTERRUPT**

- Complete current instruction

- o Save PC on stack

- o Save interrupt status

- o Jump to fixed ISR address

- o Execute ISR

- TF0

- INT1

- TF1

- Serial Port

### **I/0 INTERFACING**

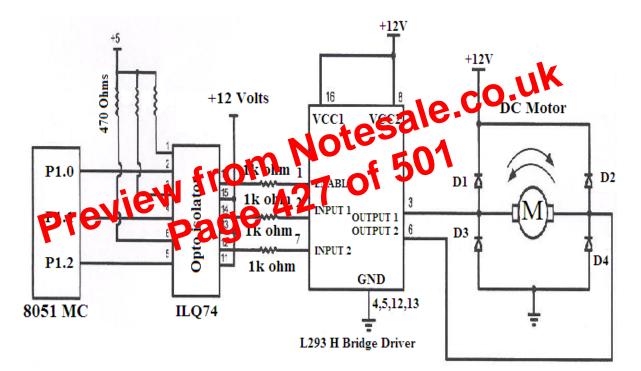

p1 is used as a general purpose port, P0 and P2 are used as data and address bus in case of external memory acess, otherwise can be used as input/output ports. P3 port contains multifunction pins. If we are using serial port, timer input pins ar external interrupt this port can not be used as port. Out of 8 bits of port p1 some can be programmed as inputs and some as outputs for example, higher nibble as output can be connected to leds & lower nibble as input can be connected to 4 switches.

### Writing code for 8051

The code can be developed in either assembly language using 8051 instructions (1) yousing a simple 'c' program by using cross compilers provided by microcontroller IDE is the KELL uVision 3. The code will be compiles/assembled linked and then executable file version verted to HEX file to dump it in Microcontroller. For that we use flash program is software power of d my manufacturer i.e. Atmel. Atmel's FLIP software is used for d money the code into mine to tontro lle e 18

### Steps for writing th

- 1. Open KEIL µVision

- 2. Go to project menu select 'new project', navigate to desired project folder and give project name in the file name window and save

- 3. Select device for target window will open, click on Atmel to drop down the menu, select AT89C51ED2 and press ok. Another window opens asking to add startup files, click no, to not to add startup.a51 file

- 4. Right click on Target1 in project Window and select 'options for target Target1' In Target select Xtal(MHz): 11.0592 Check box use on-chip ROM In output window check the box 'Create HEX file'

- 5. Go to File menu open new file to open an editor. Create your souce file(s) and use the header file "at89c51xd2.h' in the source file and save files.

- 6. Right click on Source group1 and select the option add files to group.

- 7. After adding source files go to projects-> "build Target" to build source files and create final outputs. It creates <hex file to be downloaded to target device. After successful build.

Program downloading

- 1. Set the slide swich SW2 to PROG position and press reset with SW1 on the kit.

- 2. Open atmel FLIP 2.4.2 tool

- 3. Go to device option select, select the specific device AT89C51ED2 and press OK

- 4. Go to **file-> Load hex** file, Navigate to desired hex file of the project

- 5. Go to settings option-> rs232, a window will open make sure that no other application is using com port. Click on COM select com1, set the baud rate to 115200 and click on connect

- 6. In operations flow region, check the options ERASE, BLANK CHECK, PROGRAM, VERIFY.

- 7. In the right most side of the window check the box BLJB abd set the address of BSB,EB,SBV as 00,FF and FC respectively and select option 'level0' in device SSB region.

- 8. After performing above steps click **run button** wait until the **status bar displays finished**.

- 9. After programming slide SW2 to RUN position and reset SW1 to execute the program.

Preview from Notesale.co.uk Page 181 of 501

```

display();

P3 = 0xFF;

}

} //end of main()

// get_key() function will make columns high one by one

// and calls scan() function

// on sensing a key from scan() function it

// will compare the received scan code with

// scan code lookup table and returns ASCII code

// rows are read from Port P0 is scan() function

// this function is in an eternal loop

// wiil return to main() only after getting a key

Notesale.co.uk

183 of 501

void get_key(void)

{

int i;

display();

flag = 0x00;

vhile flag

(row < 4; row + +)

if (row == 0)

temp3=0xFE;

else if(row == 1)

temp3=0xFD;

else if(row == 2)

temp3=0xFB;

else if(row == 3)

temp3=0xF7;

// make coulmn high one by one output to Port P1 and

// invoke scan() function

```

```

P0 = temp3;

```

```

scan();

```

### 6.3 ADC interfacing

/\* This program displays the ADC output of the ADC0809 IC.

Connections: CN2 port1 to CN15 connector and CN1 port0 connector to CN16 of adc block. Also Connect CN3 port2 to CN6 of LCD block. Vary pot R42 to gewt different input voltage values

\*/

#include<at89c51xd2.h> #include<stdio.h>

// LCD FUNCTION PROTOTYPE void lcd init(void); void lcd\_comm(void); void lcd\_data(void);

void delay(int);

float adc\_temp; sbit EQS

unsigned cha

Notesale.co.uk 192 of 501 unsigned char temp1; unsigned char temp2,buf[8];

void main () {

$START_ALE = 0;$

unsigned char xdata  $arr2[12] = {"ADC I/P = "};$

lcd\_init();

de ce

unsigned char i,a,temp\_hi,temp\_low;

unsigned int vtemp1,adc\_val; unsigned char temp  $msg[] = {"}$

temp1 = 0x80;position of first line lcd\_comm();

> for(i=0;i<10;i++) { temp2 = arr1[i];

// Display the data from first

// Command Writing

"};

```

{

P0 = Val;

//* Write data for clock

wise direction

Val = Val >> 1;

delay(575);

}

}

// AntiClockwise Direction

else

{

Val = 0x01;

for(i=0;i<4;i++)

{

P0 = Val;

// Write data for anticlock wise

direction

Val = Val \ll 1;

Preview from Notesale.co.uk

Page 200 of 501

```

Format: XCHG < destination > , < source >

Operation: (destination)  $\Leftrightarrow$  (Source)

Examples: XCHG Reg1, Reg2

XCHG Mem, Reg

XCHG AX, Reg16

General purpose byte or word transfer instructions

XLAT: Translate a byte in AL, using a table in memory ٠

Format: XLAT

Operation:  $PA = DS X 16_{10} + (BX) + (AL)$

$(AL) \leftarrow (PA)$

This instruction is used to translate a byte from

ithe by The instruction replaces a byte nted to by BX register in a look register with a b h up table in memory

the look up table is to be put into memory and the starting Біл uting X address of the look up table his to be loaded into BX register

ASCII value of 0-9 is 30-39 and EBCDIC is 0-9. Hence to convert EBCDIC Examples: code in ASCII, the ASCII values of the 0-9 has to be stored say from 2000H, then save 2000H in BX.

Simple input and output port transfer instructions

IN & OUT

IN : Copy a byte or word from specified port to accumulator. •

Format : IN <Accumulator>, <Source>

Example : IN AL/AX,[DX]

$(AL/AX) \leftarrow (Port)$

the contents of 8-bit port whose address is specified by DX register is transferred to 8-bit accumulator (AL/AX)

IN AL/AX, addr8

If the value in the lower nibble is greater than 9 then the AL is incremented by 06,AH is incremented by 1,the AF and CF flags are set to 1, and the higher nibble of AL is cleared to 0.

Example: 1) AL = 67 (before AAA)

AL = 07(after AAA)2) AL = 6A; AH = 00 (before AAA) A > 9, hence A + 6 = 1010 + 0110= 00010000 = 10H & AF = 1

Thus before AAA instruction AX = 006AH

DAA : Decimal adjust Accumulator

This instruction is used to convert the result of the close of two packed numbers to a valid unber, but the result has to be only in AI BCD number, but the result has to be only in AL.

If the lower nibble is g AF is set, it will add 06H to the lower after action of AL is greater than 9 or if carry flag is set, DAA nibble in AL. After a the nit ole or 05 in the lo instructor descont to AL.

The DAA instruction affects AF,CF,PF and ZF flags. The OF is undefined.

Example: AL = 53, CL = 29

ADD AL,CL ;

$$AL <- (AL) + (CL)$$

$$AL = 53 + 29 = 7C H$$

After DAA AL <- 7C + 06 H

$$AL = 82$$

✤ Example:

AL = 73 and CL = 29

ADD AL,CL

$AL \leq AL + CL$

AL <- 73 + 29

Multiplication instructions:

MUL, IMUL, AAM

o MUL : Unsigned Multiplication of byte or word.

MUL Reg. / Mem.

This instruction multiplies an unsigned byte or word by the contents of AL.

The Unsigned byte or word may be in any one of the general purpose registers or memory locations.

For Byte multiplication the most significant byte will be stored in AH register and least significant byte is stored in AL register.

For Word multiplication the most significant word of the result is stored in DX, while the least significant word of the result is stored in AX register

All the flags are modified depending upon the result of the operation. Immediate operand is not allowed in this instruction. If the most significant byte or word of result is of Control OF both will be set. Example: MUL BL CALL BX MUL : Signed Multiplication

This instruction multiplies a signed byte in source operand by a signed byte in AL register or A signed word in AX register.

The source can be a general purpose register, memory operand, index register or base register, but it cannot be an immediate data.

While using this instruction the content of accumulator and register should be sign extended binary in 2's complement form and the result is also in sign extended binary.

In case of 32-bit results, the higher order word(MSW) is stored in DX and lower order word is stored in AX

In case of 16-bit result it will be stored in AX register.

The AF, PF, SF, and ZF flags are undefined after IMUL instruction execution.

If AH and DX contains parts of 16-bit and 32-bit result respectively, CF and OF both will be set.

The AL and AX are the implicit operands in case of 8 -bits and 16-bits multiplication respectively.

The unsigned higher bits of the result are filled by sign bit and CF,AF are cleared.

Example: IMUL BL / IMUL BX

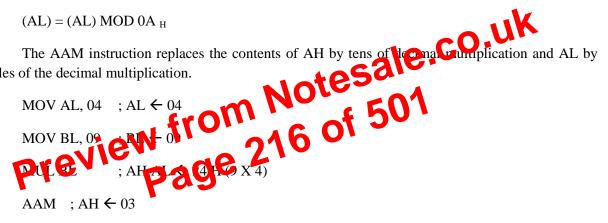

> AAM : ASCII Adjust after Multiplication

This instruction after execution, converts the product available in AL into unpacked BCD format.

The AAM instruction follows a multiplication instruction that multiplies two unpacked BCD operands, i.e., higher nibbles of the multiplication operands should be '0'. The multiplication of such operands is carried out using MUL instruction.

The result of the multiplication will be available in AX.

$(AH) = (AL) \div 0A_{H}$

singles of the decimal multiplication.

: AL ←06

ARITHMETIC **Division instructions**  **INSTRUCTIONS**

Division instructions: DIV, IDIV, AAD, CBW, CWD

o DIV : Unsigned division

DIV <reg./Mem>

This instruction performs unsigned division. It divides an unsigned word or double word by a 16bit or 8-bit operand.

The dividend must be in AX for 16-bit operation and the divisor may be specified using any one of the addressing modes except immediate.

The dividend for 32-bit operation will be in DX:AX register pair (Most significant word in DX and least significant word in AX).

All the flags are undefined for DIV instruction.

The result of division is for 16-bit number divided by 8-bit number the Quotient will be in AL register and the remainder will be in AH register similarly for 32-bit number divided by 16-bit number the Quotient will be in AX register and the remainder will be in DX register.

If the result is too big to fit into AL or AX register then Type-0 (divide by zero) interrupt is generated and the ISR for the Type zero will be executed such that correction steps are taken to accommodate the result.

For 16-bit  $\div$  8-bit

$(AL) \leftarrow (AX) \div (reg.-8)$ ; Quotient

reg.-8: 8 - bit register

$(AX) \leftarrow (DX)(AX) \div (reg.-16) ; Quotien Otesale, CO, UK$  $(DX) \leftarrow (DX)(AX) Mod reg. Q) ; Remainder Of 500$

- For 32-bit  $\div$  16-bit

- o IDIV : signed division

Example: DIV AX/

IDIV <reg./Mem>

This instruction performs signed division. It divides an signed word or double word by a signed 16-bit or 8-bit operand.

While using IDIV instruction the contents of accumulator and register should be sign extended binary.

The signed dividend must be in AX for 16-bit operation and the signed divisor may be specified using any one of the addressing modes except immediate.

The signed dividend for 32-bit operation will be in DX:AX register pair (Most significant word in DX and least significant word in AX).

All the flags are undefined for IDIV instruction.

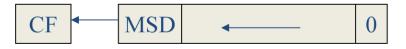

#### SHL / SAL, SHR, SAR

SHL / SAL : Shift Logical / Arithmetic Left

SHL <reg. / Mem>

$CF \leftarrow R(MSB)$ ;  $R(n+1) \leftarrow R(n)$ ;  $R(LSD) \leftarrow 0$

These instructions shift the operand word or byte bit by bit to the left and insert zeros in the newly introduced least significant bits.

The number of bits to be shifted if 1 will be specified in the instruction itself if the count is more than 1 then the count will be in CL register.

The operand to be shifted can be either register or memory location contents but cannot be immediate data.

| carry f | All the flags are affected of flag.                                                                                                                                       | lepending upon | the result.The shift | operation will const | idering using |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------|----------------------|---------------|

|         | All the flags are affected of<br>flag.<br>SHR : Shift Logical Right<br>SHR <reg. mem=""><br/>CF <math>\leftarrow</math> (M, B) , R(n) <math>\leftarrow</math> R(n)</reg.> | m              | Jotesan              | 1                    |               |

|         | SHR <reg. mem=""></reg.>                                                                                                                                                  | rom            | 3 0t 50              |                      |               |

|         |                                                                                                                                                                           |                | € 0                  |                      |               |

|         | N                                                                                                                                                                         | /ISD           |                      | LSD                  | → CF          |

These instructions shift the operand word or byte bit by bit to the right and insert zeros in the newly introduced Most significant bits.

The result of the shift operation will be stored in the register itself.

The number of bits to be shifted if 1 will be specified in the instruction itself if the count is more than 1 then the count will be in CL register.

The operand to be shifted can be either register or memory location contents but cannot be immediate data.

All the flags are affected depending upon the result. The shift operation will considering using carry flag.

SAR : Shift Logical Right

Compare one byte or word of a string data stored in data segment with that stored in extra segment.

The SI register points to the source string and DI register points to the destination string.

The CX register is decremented by one for each byte / word movement.

The SI and DI registers are automatically incremented or decremented depending on the status of DF.

$MA = (DS) X 16_{10} + (SI)$   $MA_{E} = (ES) X 16_{10} + (DI)$   $Modify flags \leftarrow (MA) - (MA_{E})$ If  $(MA) > (MA_{E})$  then CF = 0; ZF = 0; SF = 0If  $(MA) < (MA_{E})$  then CF = 1; ZF = 0; SF = 1If  $(MA) = (MA_{E})$  then CF = 0; ZF = 1; SF = 0 For byte operationIf DF = 0, then  $(DI) \leftarrow (DI) + 1$ ;  $(SI) \leftarrow (SI) \leftarrow 0$  For byte operationIf DF = 1, then  $(DI) \leftarrow (DI) + 2$ ;  $(SI) \leftarrow (SI) + 2$ If DF = 1, then  $(DI) \leftarrow (DI) + 2$ ;  $(SI) \leftarrow (SI) - 2$

SCAS / SCASB / SCASW: Scan string byte or String word

One byte or word of a string data stored in extra segment is subtracted from the contents of AL / AX and the result modifies the flags.

The DI register points to the string byte or word.

The CX register is decremented by one for each byte / word movement.

The DI register is automatically incremented or decremented depending on the status of DF.

$MA = (DS) X 16_{10} + (SI)$

$MA_E = (ES) X 16_{10} + (DI)$

Modify flags  $\leftarrow$  (AL) - (MA<sub>E</sub>) / (AX) - (MA<sub>E</sub> : MA<sub>E</sub> + 1)

The WAIT instruction is used to synchronize the 8086 processor with the external hardware such as the 8087 math processor.

➢ HLT : Halt Processing

The HLT instruction will cause the 8086 to stop the fetching and execution of the instructions. The 8086 will enter a halt state i.e., used to terminate a program.

The only ways to get processor out of Halt state are with an interrupt signal on INTR pin, an interrupt signal on NMI pin, or a valid reset signal on RESET input.

> NOP : No Operation

No operation is performed for three clock periods

This instruction simply uses up three clock cycles and increments the instruction pointer to point to the next instruction.

The NOP instruction does not affect any flag.

The NOP instruction can be used to increase the delay of a delay loop. **CO**, **UK**

When hand coding, a NOP can also be used to hold encoder a program for instruction that will d later. ESC : Escape ESC opsoid, Nen. / Reg. be added later.

$\succ$  ESC : Escape

This instruction is used to pass instructions to a coprocessor, such as the 8087 math coprocessor which shares the address and data bus with 8086

Instructions for coprocessor are represented by a 6-bit code embedded in the escape instruction.

As 8086 fetches the instructions bytes, the coprocessor also catches these bytes from the data bus and puts them in its queue, but treats all the normal 8086 instructions as NOPs and when ESC instruction is fetched by 8086, the coprocessor decodes the instruction and carries out the action specified by the 6bit code in the instruction.

In most cases 8086 treats the ESC instruction as NOP but in some cases 8086 will access a data item in memory for the coprocessor.

For ESC opcode, Mem format the data is accessed by 8087 from memory

For ESC opcode, Mem format the data is accessed by 8087 from 8086 register specified in the instruction.

LOCK : Assert Bus Lock signal

The LOCK is used as a prefix to a critical instruction which has to be executed without any disturbances to system bus from other bus masters.

When LOCK prefix is used in an instruction then during execution of this instruction the lock prefix ensures that the shared system resources are not taken over by other bus masters in the middle of the critical instruction execution.

When an instruction with LOCK prefix is executed the 8086 will assert its bus lock signal output. This signal is connected to an external bus controller device, which then prevents any other processor from taking over the system bus

LOCK affects no flags.

- Program execution transfer instructions

- > The control transfer group consists of call, jump, loop and software interrupt instructions.

- Normally a program is executed sequentially(i.e., the program instructions are executed one after the other), when a branch instruction is encountered the program execution control is transferred to the specified destination or target instructions. The transfer of program execution control is done either by changing the content of IP or by changing the contrats of P and CS.

- When the content of IP alone is modified, the control branches to new memory location in the same segment.

- When the contents of IP and CS are modified the program control branches to new memory location in indicer memory segment.

- > The control transfer is structions do not affect the flags of 8086.

- > The jump and loop instructions can be classified into conditional and unconditional instructions.

- In conditional instructions, the status of one or more flags are checked and control transfer takes place only if the specified condition is satisfied.

- > The program execution transfer instructions can be categorized as:

- Unconditional transfer instructions

- Conditional transfer instructions

- Iteration control instructions

- Software interrupt instructions

- Unconditional transfer instructions:

CALL

RET

| AD <sub>15</sub> AD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Address/ Data Bus Bidirectional<br>3 - state                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| $A_{19}S_{\overline{6}}A_{16}S_{3}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Address / Status Output 3 - State                                                               |

| <b>BHE /S7</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Bus High Enable / Output<br>Status 3- State                                                     |

| MN / MX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Minimum / Input<br>Maximum Mode<br>Control                                                      |

| RD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Read Control Output 3- State                                                                    |

| TEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Wait On Test Control Input                                                                      |

| READY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Wait State Controls Input                                                                       |

| RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | System Reset Input<br>Non - Maskable                                                            |

| NMI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Non - Maskable<br>Interrate Request Input                                                       |

| INTR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Interrupt Request Input                                                                         |

| CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | System Obek Input                                                                               |

| Prevel Pr | Non - Maskable<br>Interrors Request<br>Input<br>Input<br>System Obek<br>F 5V<br>Input<br>Ground |

| Minimum Mode Signals (MN/MX = Vcc) |          |      |  |  |  |

|------------------------------------|----------|------|--|--|--|

| Name                               | Function | Туре |  |  |  |

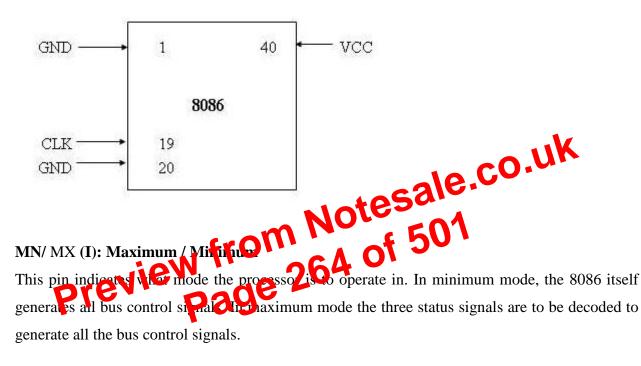

duty cycle to provide optimized internal timing. Minimum frequency of 2 MHz is required, since the design of 8086 processors incorporates dynamic cells. The maximum clock frequencies of the 8086-4, 8086 and 8086-2 are 4MHz, 5MHz and 8MHz respectively. Since the 8086 does not have on-chip clock generation

circuitry, and 8284 clock generator chip must be connected to the 8086 clock pin. The crystal connected to 8284 must have a frequency 3 times the 8086 internal frequency. The 8284 clock generation chip is used to generate READY, RESET and CLK.

#### **Minimum Mode Pins**

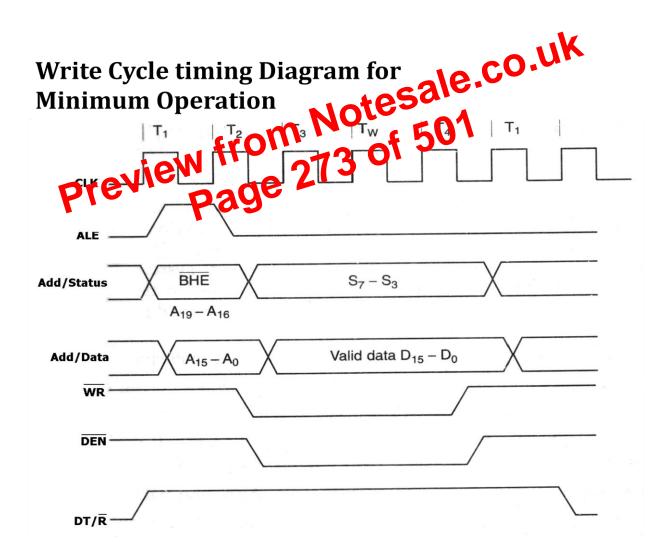

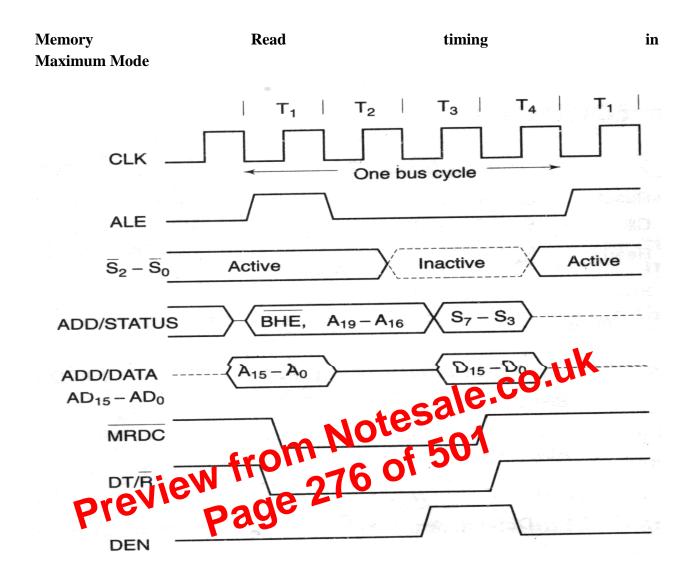

The following 8 pins function descriptions are for the 8086 in minimum mode; MN/MX = 1. The corresponding 8 pins function descriptions for maximum mode is explained later. In the bus timing diagram, data transmit / receive signal goes low (RECEIVE) for Read operation. To validate the data, DEN\* signal goes low. The Address/ Status bus carries A16 to A19 address lines during BHE\* (low) and for the remaining time carries Status information. The Address/Data bus carries A0 to A15 address information during ALE going high and for the remaining time it carries data. The RD\* line going low indicates that this is a Read operation. The curved arrows indicate the relationship between valid data and RD\* signal.

The TW is Wait time needed to synchronize the fast processor with slow memory etc. The Ready pin is checked to see whether any peripheral needs more time for data transmission.

- There does not seem to be a big difference between these methods although the book claims that there is.

- Note in either method that A<sub>0</sub> does not connect to memory and bus wire A<sub>1</sub> connects to memory pin A<sub>0</sub>, A<sub>2</sub> to A<sub>1</sub>, etc.

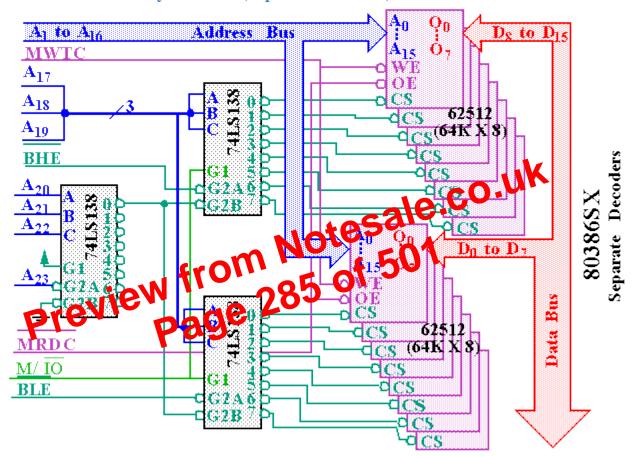

#### **80386SX 16-bit Memory Interface (Separate Decoders)**

#### **Memory Interfaces**

- See text for Separate Write Strobe scheme plus some examples of the integration of EPROM and SRAM in a complete system.

- It is just an application of what we've been covering.

- 80386DX and 80486 have 32-bit data buses and therefore 4 banks of memory.

- *32-bit*, *16-bit and 8-bit transfers are accomplished by different combinations of the bank selection signals* BE3, BE2, BE1, BE0.

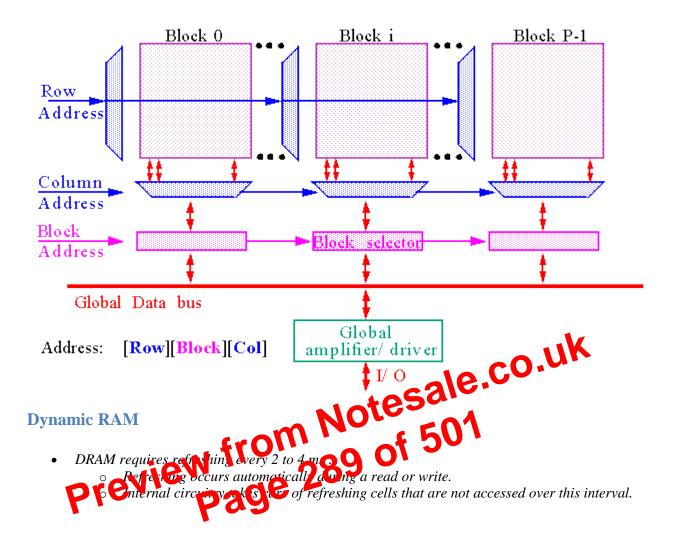

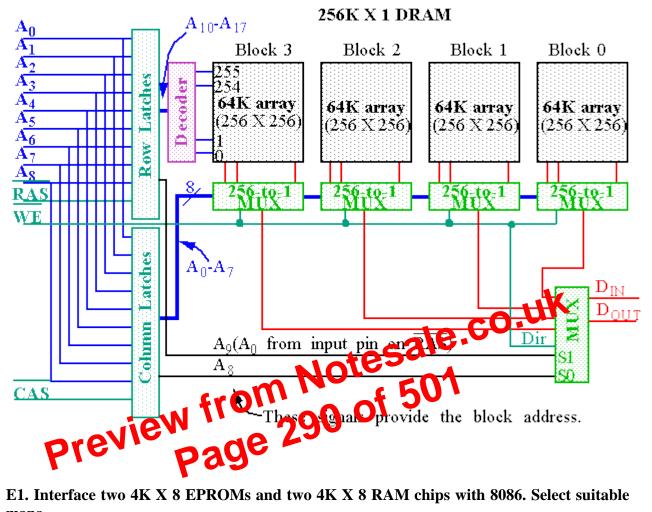

- This special refresh occurs **transparently** while other memory components operate and is called transparent refresh or cycle stealing.

- A RAS -only cycle strobes a row address into the DRAM, obtained by 7- or 8-bit binary counter.

- The capacitors are recharged for the selected row by reading the bits out internally and then writing them back.

- For a 256K X 1 DRAM with 256 rows, a refresh must occur every 15.6us (4ms/256).

- For the 8086, a read or write occurs every 800ns.

- This allows **19** memory reads/writes per refresh or **5%** of the time.

# **Dynamic RAM**

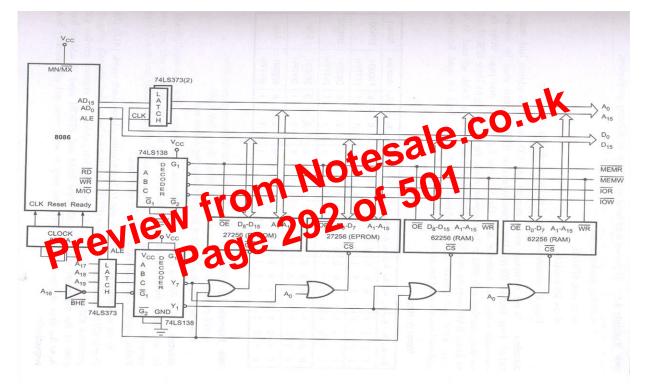

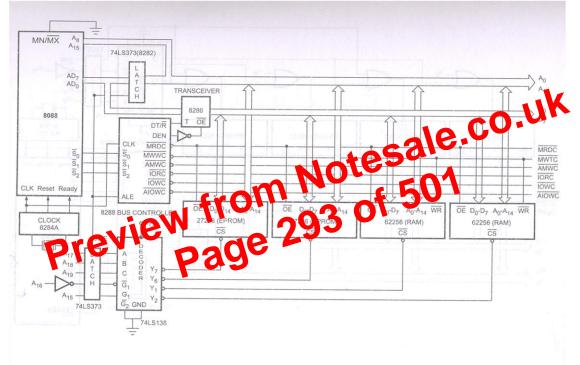

E1. Interface two 4K X 8 EPROMs and two 4K X 8 RAM chips with 8086. Select suitable maps.

First we have to write the memory map fro the problem given. It will reveal the logic to be used for decoding circuit.

Since the first instruction is fetched from FFFF0h after the microprocessor is reset, we will make that address to be present in EPROM and write the memory map as follows. And, to avoid windowing let us keep the locations to be present in the RAM as immediate addresses. Locations having addresses from FFFFH to FE000H are allocated to EPROM1 and 2. Immediate address map FDFFFH to FD000H is allocated to RAM1 and 2. The line which is differentiating EPROM from RAM if A13. Let us use it along with A0 and BHE to identify odd and even banks.